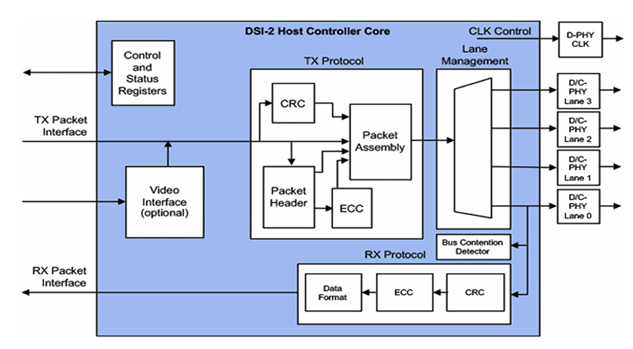

The MIPI DSI-2 (Display Serial Interface 2) IP Core is a next-generation high-speed interface standard developed by the MIPI Alliance for connecting host processors to display panels.

It builds upon the widely adopted MIPI DSI standard and introduces enhanced capabilities such as higher bandwidth, better power efficiency, support for command and video modes, and features like Display Stream Compression (DSC).