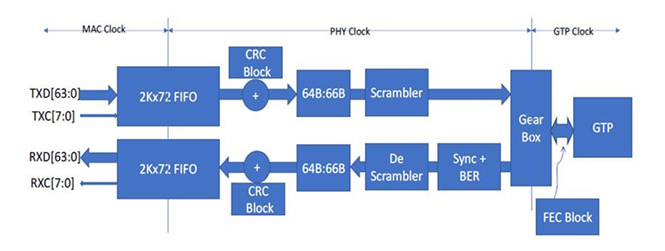

The 10G/100G MAC/PCS IP Core is a fully integrated and configurable solution that combines the Ethernet Media Access Control (MAC) and Physical Coding Sublayer (PCS) functionality into a single, high-performance IP block.

Designed in compliance with IEEE 802.3ae (10G) and IEEE 802.3ba (100G) standards, this IP core is ideal for implementing high-speed Ethernet solutions in FPGAs and ASICs for data center, telecom, AI, and networking infrastructure applications.

The IP core handles Ethernet frame encapsulation, error checking, flow control, lane alignment, and 64b/66b encoding/decoding — all with deterministic performance and minimal resource overhead.