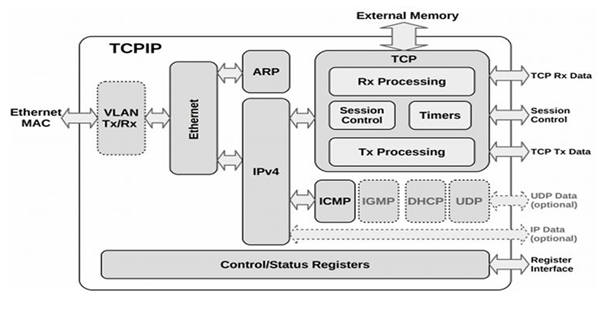

The 10G/100G TCP/IP Offload Engine (TOE) IP Core is a high-performance, scalable, and fully synthesizable hardware accelerator that offloads TCP/IP protocol stack processing from the host CPU.

It’s specifically designed for applications requiring high-throughput, low-latency data transmission, such as data centers, high-frequency trading (HFT), network appliances, and telecom infrastructure.