Wireless communication

AID-PSP

Adaptive Interactive detection- Per-Survivor Processing

Main Features

- ● MATLAB Simulation, Using FEC code

- ● Source codes (synthesizable VHDL/ Verilog/sys Gen Model) of PHY Components

- ● Design & Development of PHY Controller software

- ● PHY characterization and configuration

- ● CPM Modulator & Demodulator

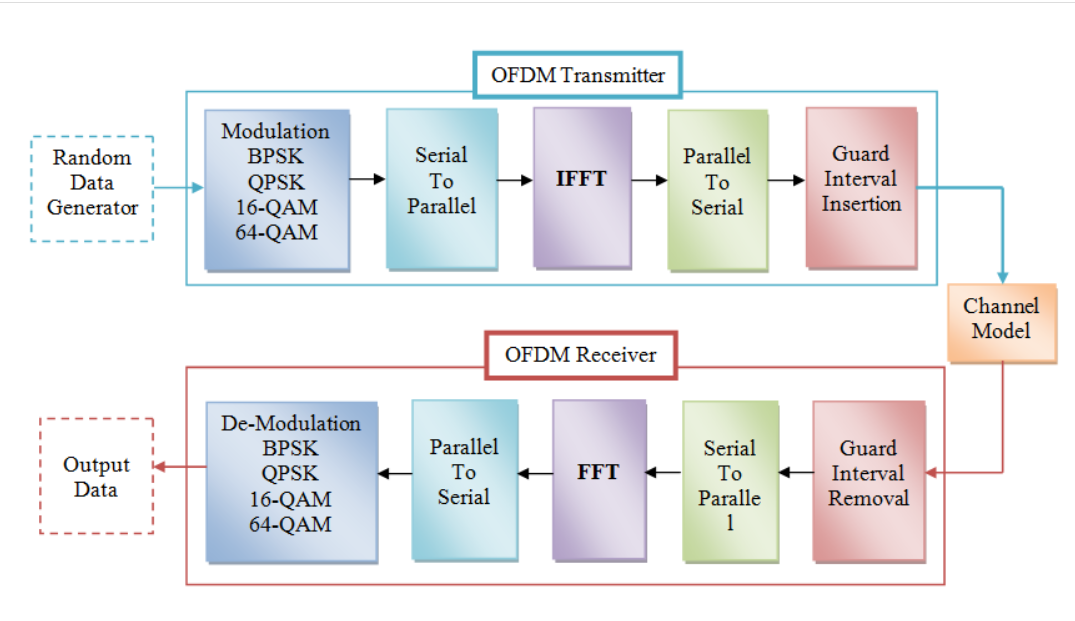

- ● DQPSK /QPSK modulator

- ● FLDPC Encoder& Decoder with different block size (encoded)

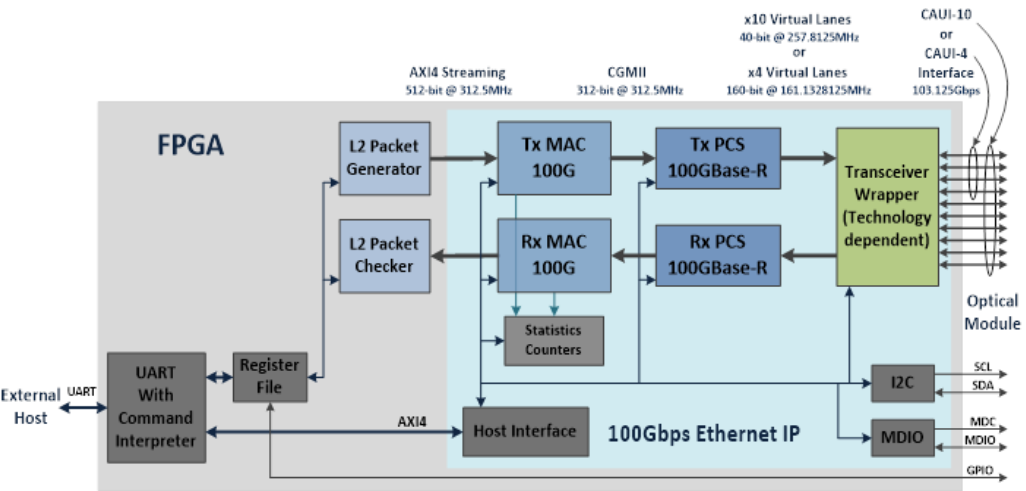

- ● FPGA Implementation

Benefits & Applications

- ● High speed & Reliable Communication

- ● High data rate enabling faster & real time communication

- ● Suitable for High performance computing requirement

- ● Configurable to accommodate multiple demodulation schemes, decoding algorithms

- ● Helpful in joint data detection and adaptive parameter filtering

Technical Specifications

PHY Components

1: CPM Modulator/ Demodulator

- Data Rate

- Modulation Index

- Baseband Filtering

- BT product

- Burst size

- Output format

- Mode of Transmission

- Packet length

- Preamble size

- Channel

- Normalized Doppler offset

- SNR @ BER 10^-3(Rayleigh Channel)

- 200kbps to 10 Mbps in steps of 100Kbps

- Programmable up to 0.5

- Gaussian/Raised cosine/Root raised cosine

- 0.1/0.25/0.3

- 100us to 2000us in steps of 100us

- Baseband IQ data

- Burst or Continuous

- Programmable

- <64'

- Rayleigh, Rician with K factor=10

- 2%

- ≤25dB for slow & flat Rayleigh channel (Partial response CPM, BT=0.25, Gaussian Pulse shaping)

2: DQPSK/QPSK modulator

- Data Rate

- Differential Encoding

- Baseband Filtering

- Roll off factor

- 200kbps to 10 Mbps in steps of 100Kbps

- On/Off

- Root raised cosine

- 0.1/0.25/0.3/0.35/0.4/0.5 (programmable)

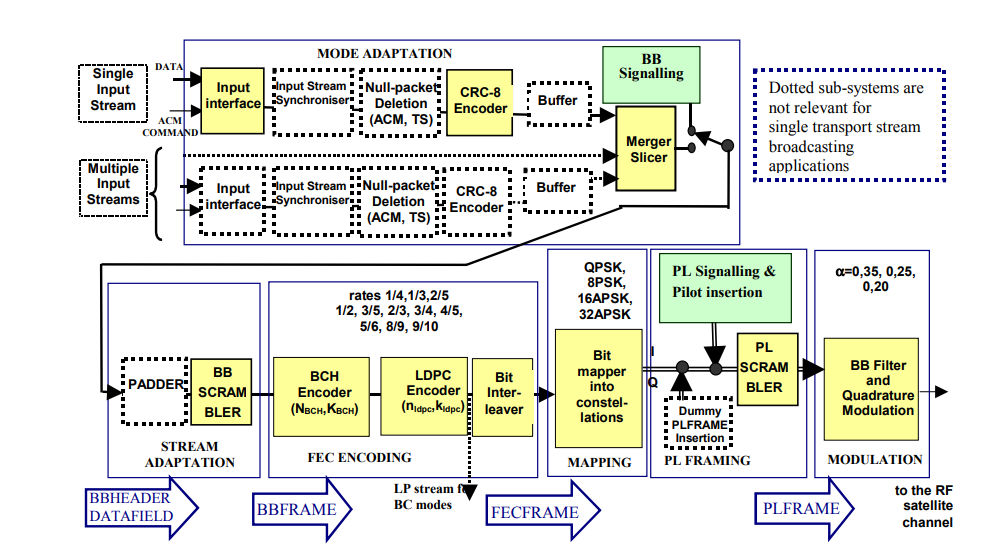

3: LDPC Encoder/Decoder

- Block size(encoded)

- Code rate

- Operating clock

- Throughput

- Max no iterations

- Soft Input/output LLR

- 128, 256,512,1024,2048,4096,8192,16384

- 1/3,1/2, 2/3, 3/4, 4/5, 5/6, 6/7, 7/8, 8/9, 9/10

- 200MHz

- 50MHz

- Programmable up to 40

- 6-bits